Data Sheet

Please submit RFQ for AD9649BCPZ-20 or <a href="mailto-us:sales@ovaga.com"><u>Email to-us:sales@ovaga.com</u></a> We will contact you in 12 hours.

**RFO**

## **General Description**

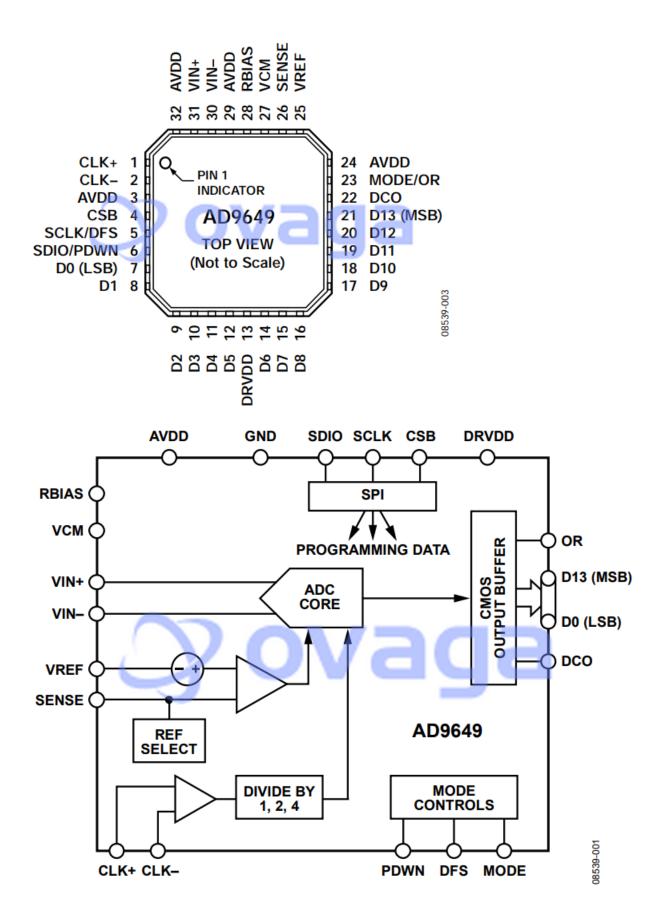

The AD9649 is a monolithic, single channel 1.8 V supply, 14-bit, 20/40/65/80 MSPS analog-to-digital converter (ADC). It features a high performance sample-and-hold circuit and an on-chip volt-age reference.

The product uses multistage differential pipeline architecture with output error correction logic to provide 14-bit accuracy at 80 MSPS data rates and to guarantee no missing codes over the full operating temperature range.

The ADC contains several features designed to maximize flexibility and minimize system cost, such as programmable clock and data alignment and programmable digital test pattern generation. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI).

A differential clock input with optional 1, 2, or 4 divide ratios controls all internal conversion cycles.

The digital output data is presented in offset binary, gray code, or twos complement format. A data output clock (DCO) is provided to ensure proper latch timing with receiving logic. Both 1.8 V and 3.3 V CMOS levels are supported.

The AD9649 is available in a 32-lead RoHS-compliant LFCSP and is specified over the industrial temperature range ( $-40^{\circ}$ C to  $+85^{\circ}$ C).

## PRODUCT HIGHLIGHTS

## APPLICATIONS

The AD9649 operates from a single 1.8 V analog power supply and features a separate digital output driver supply to accommodate 1.8 V to 3.3 V logic families.

The sample-and-hold circuit maintains excellent performance for input frequencies up to 200 MHz and is designed for low cost, low power, and ease of use.

A standard serial port interface (SPI) supports various product features and functions, such as data output formatting, internal clock divider, power-down, DCO, data output (D13 to D0) timing and offset adjustments, and voltage reference modes.

The AD9649 is packaged in a 32-lead RoHS-compliant LFCSP that is pin compatible with the AD9629 12-bit ADC and the AD9609 10-bit ADC, enabling a simple migration path between 10-bit and 14-bit converters sampling from 20 MSPS to 80 MSPS.

**Features**

**Application**

1.8 V analog supply operation

Communications

1.8 V to 3.3 V output supply

Diversity radio systems

**SNR**

Multimode digital receivers

74.3 dBFS at 9.7 MHz input

GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA

71.5 dBFS at 200 MHz input

Smart antenna systems

SFDR

Battery-powered instruments

93 dBc at 9.7 MHz input

Handheld scope meters

80 dBc at 200 MHz input

Portable medical imaging

Low power

Ultrasound

45 mW at 20 MSPS

Radar/LIDAR

87 mW at 80 MSPS

Differential input with 700 MHz bandwidth

On-chip voltage reference and sample-and-hold circuit

2 V

р-р

differential analog input

Serial port control options

Offset binary, gray code, or twos complement data format

See data sheet for additional features

**Related Products**

ADAS3022BCPZ

Analog Devices, Inc

LFCSP-40

AD7266BSUZ

Analog Devices, Inc

TQPF-32

AD574AJNZ

Analog Devices, Inc

PDIP-28

AD7938BSUZ Analog Devices, Inc TQFP-32

AD7124-8BCPZ-RL7

Analog Devices, Inc

LFCSP-32

AD7401YRWZ

Analog Devices, Inc

SOIC-16

AD7192BRUZ-REEL

Analog Devices, Inc

TSSOP-24

AD9680BCPZ-500

Analog Devices, Inc

LFCSP-64